prodotti Kategorija

- FM trasmettitur

- 0-50w 50w-1000w 2kw-10kw 10kw +

- Transmiter TV

- 0-50w 50-1kw 2kw-10kw

- FM antenna

- TV antenna

- antenna Aċċessorju

- kejbil konnettur Power isplitter Tagħbija finta

- RF transistor

- Power Supply

- Tagħmir awdjo

- DTV Front End Tagħmir

- rabta Sistema

- sistema STL Link Sistema microwave

- FM Radju

- Power Meter

- Prodotti oħra

- Speċjali għall-Coronavirus

prodotti Tags

Fmuser Siti

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> Afrikans

- sq.fmuser.net -> Albaniż

- ar.fmuser.net -> Għarbi

- hy.fmuser.net -> Armenjan

- az.fmuser.net -> Ażerbajġan

- eu.fmuser.net -> Bask

- be.fmuser.net -> Belarussu

- bg.fmuser.net -> Bulgaru

- ca.fmuser.net -> Katalan

- zh-CN.fmuser.net -> Ċiniż (Simplifikat)

- zh-TW.fmuser.net -> Ċiniż (Tradizzjonali)

- hr.fmuser.net -> Kroat

- cs.fmuser.net -> Ċek

- da.fmuser.net -> Daniż

- nl.fmuser.net -> Olandiż

- et.fmuser.net -> Estonjan

- tl.fmuser.net -> Filippin

- fi.fmuser.net -> Finlandiż

- fr.fmuser.net -> Franċiż

- gl.fmuser.net -> Galizjan

- ka.fmuser.net -> Ġorġjan

- de.fmuser.net -> Ġermaniż

- el.fmuser.net -> Grieg

- ht.fmuser.net -> Creole Ħaiti

- iw.fmuser.net -> Ebrajk

- hi.fmuser.net -> Ħindi

- hu.fmuser.net -> Ungeriż

- is.fmuser.net -> Iżlandiż

- id.fmuser.net -> Indoneżjan

- ga.fmuser.net -> Irlandiż

- it.fmuser.net -> Taljan

- ja.fmuser.net -> Ġappuniż

- ko.fmuser.net -> Korean

- lv.fmuser.net -> Latvjan

- lt.fmuser.net -> Litwan

- mk.fmuser.net -> Maċedonjan

- ms.fmuser.net -> Malajan

- mt.fmuser.net -> Malti

- no.fmuser.net -> Norveġiż

- fa.fmuser.net -> Persjan

- pl.fmuser.net -> Pollakk

- pt.fmuser.net -> Portugiż

- ro.fmuser.net -> Rumen

- ru.fmuser.net -> Russu

- sr.fmuser.net -> Serb

- sk.fmuser.net -> Slovakk

- sl.fmuser.net -> Sloven

- es.fmuser.net -> Spanjol

- sw.fmuser.net -> Swaħili

- sv.fmuser.net -> Svediż

- th.fmuser.net -> Tajlandiż

- tr.fmuser.net -> Tork

- uk.fmuser.net -> Ukrain

- ur.fmuser.net -> Urdu

- vi.fmuser.net -> Vjetnamiż

- cy.fmuser.net -> Welsh

- yi.fmuser.net -> Jiddix

Transisters PMOS u NMOS

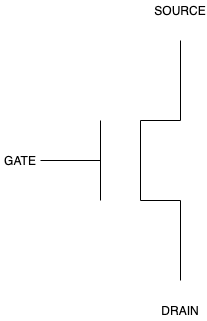

Il-mikroproċessuri huma mibnija minn transisters. B'mod partikolari, huma mibnija minn transisters MOS. MOS huwa akronimu għal Metal-Oxide Semiconductor. Hemm żewġ tipi ta 'transisters MOS: pMOS (pożittiv-MOS) u nMOS (negattiv-MOS). Kull pMOS u nMOS jiġi mgħammar bi tliet komponenti ewlenin: il-bieb, is-sors, u l-fossa.

Biex tifhem sew kif joperaw pMOS u nMOS, huwa importanti li l-ewwel jiġu definiti xi termini:

ċirkwit magħluq: Dan ifisser li l-elettriku qed jiċċirkola mill-bieb għas-sors.

ċirkwit miftuħ: Dan ifisser li l-elettriku mhux qed joħroġ mill-bieb għas-sors; iżda pjuttost, l-elettriku qed joħroġ mill-bieb għall-fossa.

Meta transistor nMOS jirċievi vultaġġ mhux negliġibbli, il-konnessjoni mis-sors għall-fossa taġixxi bħala wajer. L-elettriku se joħroġ mis-sors għall-fossa mingħajr inibizzjoni - dan jissejjaħ ċirkwit magħluq. Min-naħa l-oħra, meta transistor nMOS jirċievi vultaġġ ta 'madwar 0 volt, il-konnessjoni mis-sors għall-fossa tinkiser u dan jissejjaħ ċirkwit miftuħ.

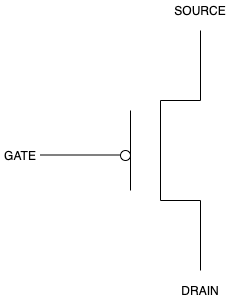

It-transistor tat-tip p jaħdem eżattament kontra t-transistor tat-tip n. Billi l-nMOS se jifforma ċirkwit magħluq mas-sors meta l-vultaġġ ma jkunx negliġibbli, il-pMOS se jifforma ċirkwit miftuħ mas-sors meta l-vultaġġ ma jkunx negliġibbli.

Kif tistgħu taraw fl-immaġni tat-transistor pMOS murija hawn fuq, l-unika differenza bejn transistor pMOS u transistor nMOS hija ċ-ċirku żgħir bejn il-bieb u l-ewwel bar. Dan iċ-ċirku jaqleb il-valur mill-vultaġġ; għalhekk, jekk il-bieb jibgħat vultaġġ rappreżentattiv ta 'valur ta' 1, allura l-inverter se jibdel l-1 għal 0 u jikkawża li ċ-ċirkwit jiffunzjona kif xieraq.

Peress li pMOS u nMOS jiffunzjonaw b'mod oppost - b'mod kumplimentari - meta ngħaqqdu t-tnejn f'ċirkwit MOS ġgant wieħed, jissejjaħ ċirkwit cMOS, li jirrappreżenta semikonduttur kumplimentari tal-ossidu tal-metall.

Jutilizzaw iċ-Ċirkwiti MOS

Nistgħu ngħaqqdu ċirkwiti pMOS u nMOS sabiex nibnu strutturi aktar kumplessi msejħa GATES, b'mod aktar speċifiku: xtiebi loġiċi. Diġà daħħalna l-kunċett ta’ dawn il-funzjonijiet loġiċi u t-tabelli tal-verità assoċjati tagħhom fil-blog preċedenti, li tista’ ssib billi tikklikkja hawn.

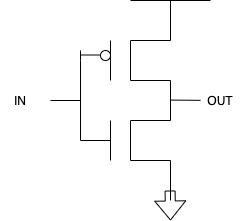

Nistgħu nwaħħal transistor pMOS li jgħaqqad mas-sors u transistor nMOS li jgħaqqad mal-art. Dan se jkun l-ewwel eżempju tagħna ta 'transistor cMOS.

Dan it-transistor cMOS jaġixxi b'mod simili għall-funzjoni loġika MHUX.

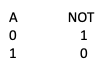

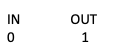

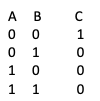

Ejja nagħtu ħarsa lejn it-tabella tal-verità MHUX:

Fit-tabella tal-verità MHUX, kull valur input: A huwa maqlub. X'jiġri miċ-ċirkwit t'hawn fuq?

Ukoll, ejja nimmaġinaw li l-input huwa 0.

L-0 jidħol u jmur kemm 'il fuq kif ukoll 'l isfel mill-wajer kemm għall-pMOS (fuq) kif ukoll għall-nMOS (ta' isfel). Meta l-valur 0 jilħaq il-pMOS, jinqaleb għal 1; għalhekk, il-konnessjoni mas-sors hija magħluqa. Dan se jipproduċi valur loġiku ta '1 sakemm il-konnessjoni mal-art (fossa) ma tkunx magħluqa wkoll. Ukoll, peress li t-transisters huma komplementari, nafu li t-transistor nMOS mhux se jaqleb il-valur; għalhekk, tieħu l-valur 0 kif inhu u se — għalhekk — toħloq ċirkwit miftuħ għall-art (drain). Għalhekk, valur loġiku ta '1 huwa prodott għall-bieb.

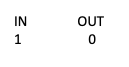

X'jiġri jekk 1 huwa l-valur IN? Ukoll, wara l-istess passi bħal hawn fuq, il-valur 1 jintbagħat kemm lill-pMOS kif ukoll lill-nMOS. Meta l-valur jiġi riċevut mill-pMOS, il-valur jinqaleb għal 0; għalhekk, il-konnessjoni mas-SORS hija miftuħa. Meta l-valur jiġi riċevut mill-nMOS, il-valur ma jinqalebx; għalhekk, il-valur jibqa '1. Meta valur ta' 1 jiġi riċevut mill-nMOS, il-konnessjoni tingħalaq; għalhekk, il-konnessjoni mal-art hija magħluqa. Dan se jipproduċi valur loġiku ta '0.

It-tqegħid taż-żewġ settijiet ta' input/output flimkien jagħti:

Huwa pjuttost faċli li wieħed jara li din it-tabella tal-verità hija eżattament l-istess bħal dik li MHUX tipproduċi l-funzjoni loġika. Għalhekk, dan huwa magħruf bħala bieb MHUX.

Nistgħu nużaw dawn iż-żewġ transistors sempliċi biex nagħmlu strutturi aktar ikkumplikati? Assolutament! Sussegwentement, se nibnu gate NOR u gate OR.

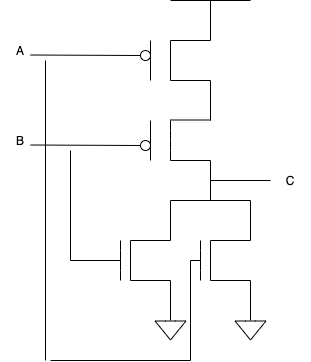

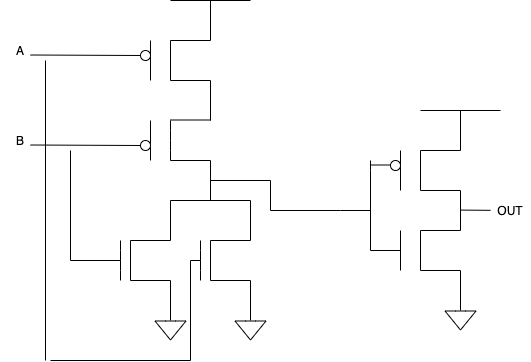

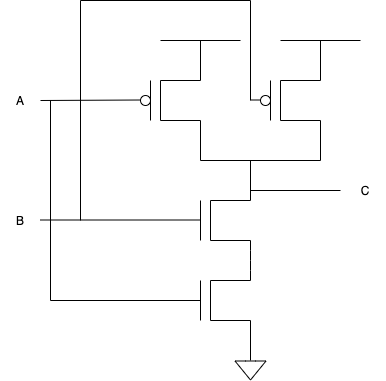

Dan iċ-ċirkwit juża żewġ transistors pMOS fil-parti ta 'fuq u żewġ transisters nMOS fil-qiegħ. Għal darb'oħra, ejja nħarsu lejn l-input għall-bieb biex tara kif iġib ruħu.

Meta A huwa 0 u B huwa 0, dan il-bieb se jaqleb iż-żewġ valuri għal 1 meta jilħqu t-transistors pMOS; madankollu, it-transistors nMOS se jżommu t-tnejn il-valur ta '0. Dan iwassal lill-bieb biex jipproduċi valur ta' 1.

Meta A huwa 0 u B huwa 1, dan il-bieb se taqleb iż-żewġ valuri meta jilħqu t-transistors pMOS; għalhekk, A se jinbidel għal 1 u B se jinbidel għal 0. Dan mhux se jwassal għas-sors; peress li ż-żewġ transistors jeħtieġu ċirkwit magħluq sabiex jgħaqqdu l-input mas-sors. It-transisters nMOS ma jaqilbux il-valuri; għalhekk, l-nMOS assoċjat ma 'A se jipproduċi 0, u l-nMOS assoċjat ma' B se jipproduċi 1; għalhekk, l-nMOS assoċjat ma 'B se jipproduċi ċirkwit magħluq mal-art. Dan iwassal lill-bieb biex jipproduċi valur ta '0.

Meta A huwa 1 u B huwa 0, dan il-bieb se taqleb iż-żewġ valuri meta jilħqu t-transistors pMOS; għalhekk, A se jinbidel għal 0 u B se jinbidel għal 1. Dan mhux se jwassal għas-sors; peress li ż-żewġ transistors jeħtieġu ċirkwit magħluq sabiex jgħaqqdu l-input mas-sors. It-transisters nMOS ma jaqilbux il-valuri; għalhekk, l-nMOS assoċjat ma 'A se jipproduċi 1, u l-nMOS assoċjat ma' B se jipproduċi 0; għalhekk, l-nMOS assoċjati ma 'Awill jipproduċu ċirkwit magħluq għall-art. Dan iwassal lill-bieb biex jipproduċi valur ta '0.

Meta A huwa 1 u B huwa 1, dan il-bieb se taqleb iż-żewġ valuri meta jilħqu t-transistors pMOS; għalhekk, A se jinbidel għal 0 u B se jinbidel għal 0. Dan mhux se jwassal għal sors; peress li ż-żewġ transistors jeħtieġu ċirkwit magħluq sabiex jgħaqqdu l-input mas-sors. It-transisters nMOS ma jaqilbux il-valuri; għalhekk, l-nMOS assoċjat ma 'A se jipproduċi 1, u l-nMOS assoċjat ma' B se jipproduċi 1; għalhekk, l-nMOS assoċjati ma 'A u l-nMOS assoċjati ma' B se jipproduċu ċirkwit magħluq mal-art. Dan iwassal lill-bieb biex jipproduċi valur ta '0.

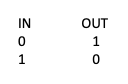

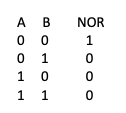

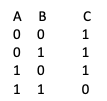

Għalhekk, it-tabella tal-verità tal-bieb hija kif ġej:

Sadanittant, it-tabella tal-verità tal-funzjoni loġika NOR hija kif ġej:

Għalhekk, ikkonfermajna li dan il-bieb huwa bieb NOR għaliex jaqsam it-tabella tal-verità tiegħu mal-funzjoni loġika NOR.

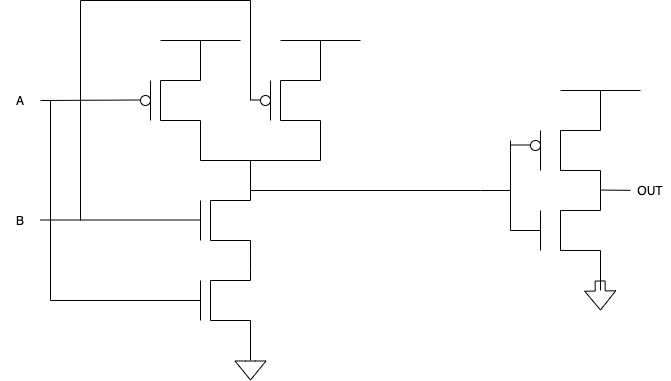

Issa, se npoġġu ż-żewġ gradi, li ħloqna s'issa, flimkien sabiex nipproduċu gate OR. Ftakar, NOR stands għal NOT OR; għalhekk, jekk inqalbu xatba diġà maqluba, aħna se terġa 'lura l-oriġinal. Ejja npoġġu dan għall-prova sabiex narawha fl-azzjoni.

Dak li għamilna hawn hu li ħadna l-bieb NOR minn qabel u applikajna bieb MHUX għall-output. Kif urejna hawn fuq, il-bieb NOT jieħu valur ta '1 u joħroġ 0, u l-bieb NOT jieħu valur ta' 0 u joħroġ 1.

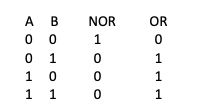

Dan se jieħu l-valuri tal-bieb NOR u jikkonverti l-0s kollha għal 1s u 1s għal 0s. Għalhekk, it-tabella tal-verità se tkun kif ġej:

Jekk tixtieq aktar prattika li tittestja dawn il-gradi, tħossok liberu li tipprova l-valuri t'hawn fuq għalik innifsek u ara li l-bieb jipproduċi riżultati ekwivalenti!

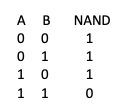

Jiena nsostni li dan huwa xatba NAND, imma ejja nittestjaw it-tabella tal-verità ta 'dan il-bieb biex tiddetermina jekk hux verament xatba NAND.

Meta A huwa 0 u B huwa 0, il-pMOS ta' A jipproduċi 1, u l-nMOS ta' A jipproduċi 0; għalhekk, dan il-bieb se jipproduċi 1 loġiku peress li huwa konness mas-sors b'ċirkwit magħluq u skonnettjat mill-art b'ċirkwit miftuħ.

Meta A huwa 0 u B huwa 1, il-pMOS ta' A jipproduċi 1, u l-nMOS ta' A jipproduċi 0; għalhekk, dan il-bieb se jipproduċi 1 loġiku peress li huwa konness mas-sors b'ċirkwit magħluq u skonnettjat mill-art b'ċirkwit miftuħ.

Meta A huwa 1 u B huwa 0, il-pMOS ta' B jipproduċi 1, u l-nMOS ta' B jipproduċi 0; għalhekk, dan il-bieb se jipproduċi 1 loġiku peress li huwa konness mas-sors b'ċirkwit magħluq u skonnettjat mill-art b'ċirkwit miftuħ.

Meta A huwa 1 u B huwa 1, il-pMOS ta' A jipproduċi 0, u l-nMOS ta' A jipproduċi 1; għalhekk, irridu niċċekkjaw il-pMOS u n-nMOS ta 'B, ukoll. Il-pMOS ta' B se jipproduċi 0, u n-nMOS ta' B jipproduċi 1; għalhekk, dan il-bieb se jipproduċi 0 loġiku peress li huwa skonnettjat mis-sors b'ċirkwit miftuħ u konness mal-art b'ċirkwit magħluq.

It-tabella tal-verità hija kif ġej:

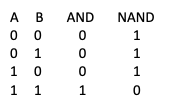

Sadanittant, it-tabella tal-verità tal-funzjoni loġika NAND hija kif ġej:

Għalhekk, ivverifikajna li dan huwa, tabilħaqq, gate NAND.

Issa, kif nibnu gate AND? Ukoll, aħna se nibnu gate AND bl-istess mod eżatt kif bnejna gate OR minn gate NOR! Aħna se nwaħħal inverter!

Peress li kulma għamilna hija applikata funzjoni NOT għall-output ta 'bieb NAND, it-tabella tal-verità tidher bħal din:

Għal darb'oħra, jekk jogħġbok ivverifika biex tiżgura li dak li qed ngħidlek huwa l-verità.

Illum, koprejna x'inhuma t-transistors pMOS u nMOS kif ukoll kif tużahom biex nibnu strutturi aktar kumplessi! Nispera li sibt dan il-blog informattiv. Jekk tixtieq taqra l-blogs preċedenti tiegħi, issib il-lista hawn taħt.